今天來(lái)科普下芯片設(shè)計(jì)的流程以及設(shè)計(jì)需要的工具。芯片設(shè)計(jì)過(guò)程可分為兩個(gè)部分, 芯片設(shè)計(jì)與制造兩個(gè)環(huán)節(jié)。

芯片設(shè)計(jì)

芯片設(shè)計(jì)階段會(huì)明確芯片的用途、規(guī)格和性能表現(xiàn),芯片設(shè)計(jì)可分為規(guī)格定義、系統(tǒng)級(jí)設(shè)計(jì)、前端設(shè)計(jì)和后端設(shè)計(jì)4大過(guò)程。

1. 規(guī)格定義

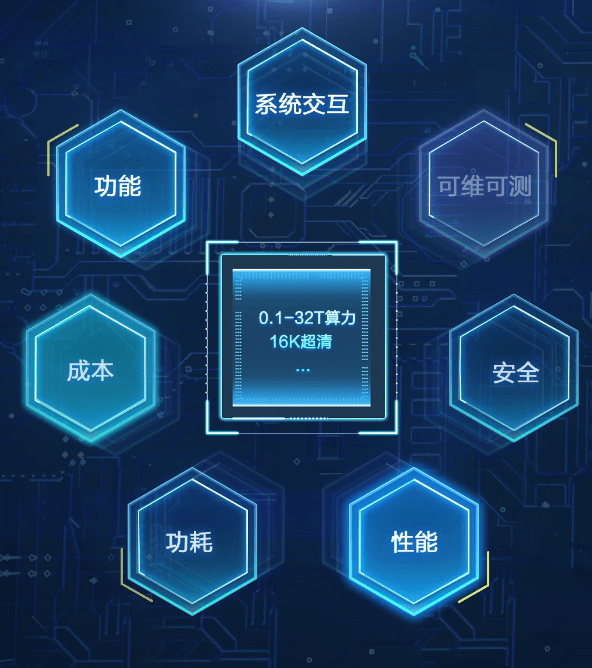

工程師在芯片設(shè)計(jì)之初,會(huì)做好芯片的需求分析、完成產(chǎn)品規(guī)格定義,以確定設(shè)計(jì)的整體方向。例如:成本控制在什么水平,需要多少TOPS的AI算力,是否功耗敏感,支持哪些聯(lián)接方式,系統(tǒng)需要遵循的安全等級(jí)等。

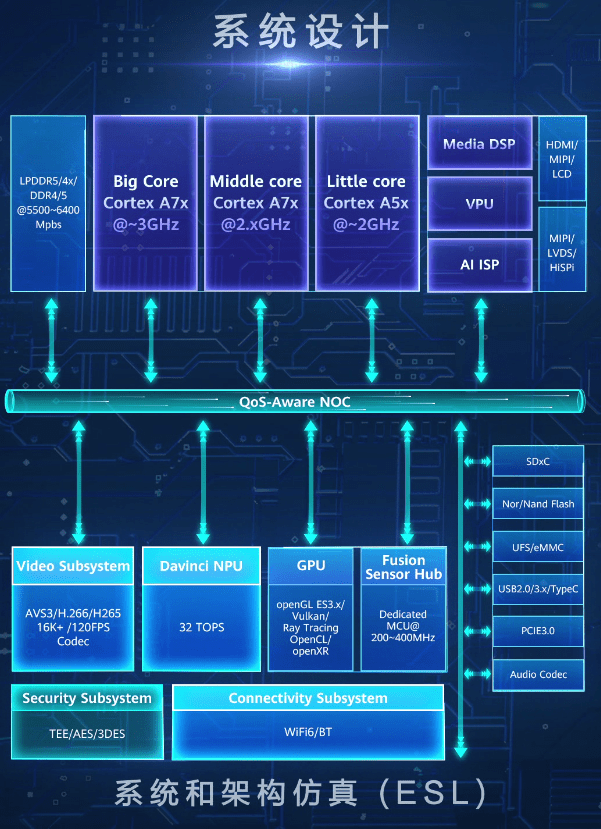

2. 系統(tǒng)設(shè)計(jì)

基于前期的規(guī)格定義,明確芯片架構(gòu)、業(yè)務(wù)模塊、供電等系統(tǒng)級(jí)設(shè)計(jì),例如CPU、GPU、NPU、RAM、聯(lián)接、接口等。芯片設(shè)計(jì)需要綜合考量芯片的系統(tǒng)交互、功能、成本、功耗、性能、安全及可維可測(cè)等綜合要素。

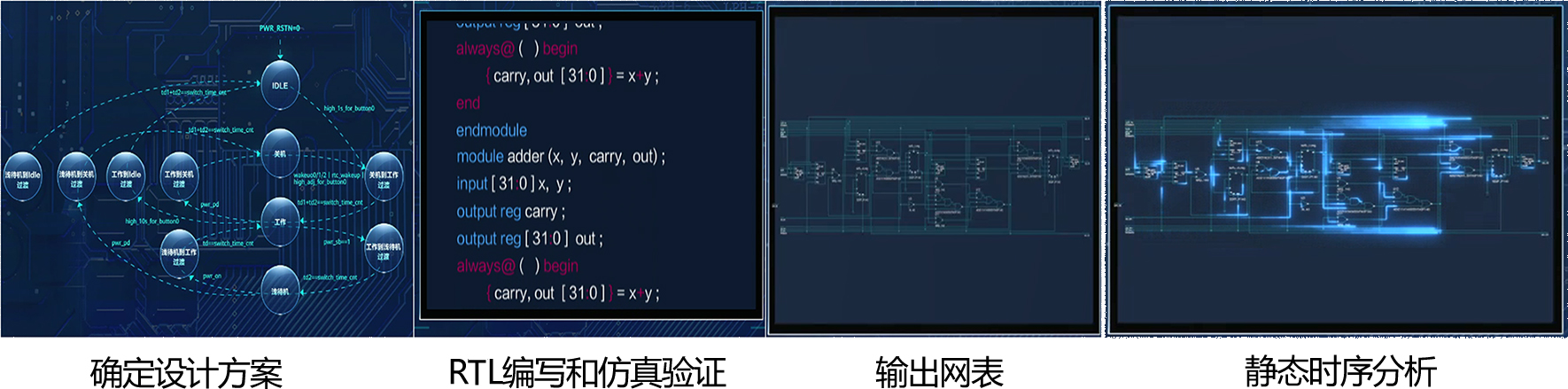

3. 前端設(shè)計(jì)

前端設(shè)計(jì)時(shí),設(shè)計(jì)人員根據(jù)系統(tǒng)設(shè)計(jì)確定的方案,針對(duì)各模塊開(kāi)展具體的電路設(shè)計(jì),使用專門(mén)的硬件描述語(yǔ)言(Verilog或VHDL),對(duì)具體的電路實(shí)現(xiàn)進(jìn)行RTL(Register Transfer Level)級(jí)別的代碼描述。代碼生成后,就需要嚴(yán)格按照已制定的規(guī)格標(biāo)準(zhǔn),通過(guò)仿真驗(yàn)證來(lái)反復(fù)檢驗(yàn)代碼設(shè)計(jì)的正確性。之后,用邏輯綜合工具,把用硬件描述語(yǔ)言寫(xiě)成的RTL級(jí)的代碼轉(zhuǎn)成門(mén)級(jí)網(wǎng)表(NetList),以確保電路在面積、時(shí)序等目標(biāo)參數(shù)上達(dá)到標(biāo)準(zhǔn)。邏輯綜合完成后需要進(jìn)行靜態(tài)時(shí)序分析,套用特定的時(shí)序模型,針對(duì)特定電路分析其是否違反設(shè)計(jì)者給定的時(shí)序限制。整個(gè)設(shè)計(jì)流程是一個(gè)迭代的流程,任何一步不能滿足要求都需要重復(fù)之前的步驟,甚至重新設(shè)計(jì)RTL代碼。

推薦閱讀:芯片設(shè)計(jì)5五部曲:

聲光魔法師——模擬IC

圖靈藝術(shù)師——數(shù)字IC

戰(zhàn)略規(guī)劃師——算法仿真

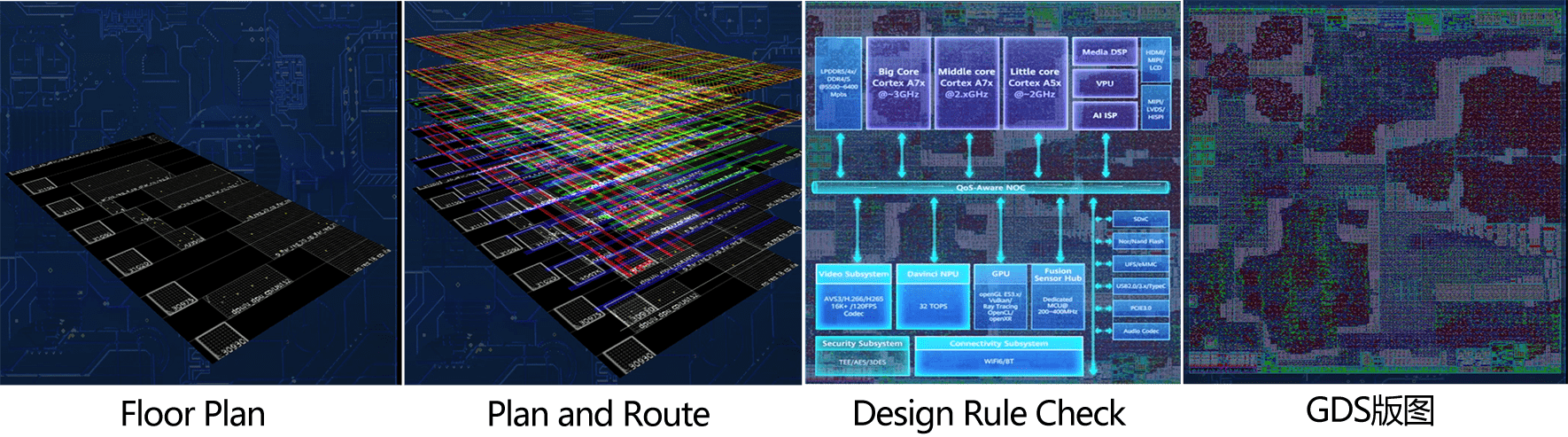

4. 后端設(shè)計(jì)

后端設(shè)計(jì)是先基于網(wǎng)表,在給定大小的硅片面積內(nèi),對(duì)電路進(jìn)行布局(Floor Plan)和繞線(Place and Route),再對(duì)布線的物理版圖進(jìn)行功能和時(shí)序上的各種驗(yàn)證(Design Rule Check、Layout Versus Schematic等),后端設(shè)計(jì)也是一個(gè)迭代的流程,驗(yàn)證不滿足要求則需要重復(fù)之前的步驟,最終生成用于芯片生產(chǎn)的GDS(Geometry Data Standard)版圖。

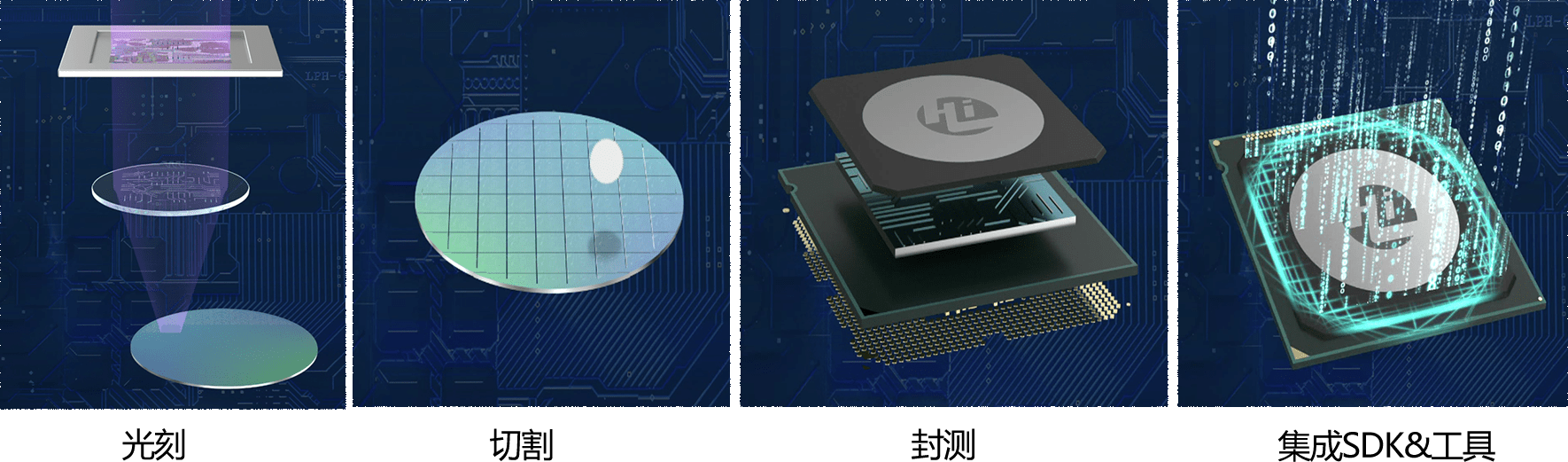

芯片制造:點(diǎn)“沙”成金

芯片制造環(huán)節(jié)中,芯片是如何被“點(diǎn)沙成金”的呢?看似無(wú)關(guān)且不起眼的沙子,富含二氧化硅,而二氧化硅通過(guò)高溫加熱、純化、過(guò)濾等工藝,可從中提取出硅單質(zhì),然后經(jīng)特殊工藝鑄造變成純度極高的塊狀單晶硅,稱作單晶硅棒(Crystal Ingot)。

單晶硅棒根據(jù)用途被切割成0.5mm-1.5mm厚度的薄片,即成為芯片的基本原料,硅晶圓片,這便是“晶圓(Wafer)”。

晶圓(wafer),相當(dāng)于芯片的“地基”,提到晶圓一般會(huì)提到尺寸如8寸或12寸,尺寸是硅晶圓的單位

單晶(monocrystalline)具有原子一個(gè)個(gè)緊密排列的特性,可以形成平整的原子表層,使用單晶做晶圓,可以使后續(xù)添加的原則和基板結(jié)合更固定

晶圓(Wafer)經(jīng)過(guò)拋光處理及一系列嚴(yán)格篩查后,投入第一階段的生產(chǎn)工藝,即前段生產(chǎn)(Front End Of Line)。這一階段主要完成集成晶體管的制造,包括光刻、薄膜、刻蝕、清洗、注入等幾大模塊的工藝。

第一階段前段生產(chǎn)(FEOL)完成后,接著開(kāi)始后段生產(chǎn)(BEOL),BEOL由沉積無(wú)摻雜的氧化硅(也就是硅玻璃)開(kāi)始,通孔由金屬鎢填充,然后制作晶體管間的電連線,最終得到滿足芯片要求的晶圓。獲得晶圓后,用圓鋸切割芯片,嵌入封裝中。芯片使用引線與封裝的引腳結(jié)合,封裝蓋子保護(hù)芯片不受外界灰塵污染。一顆融合人類智慧結(jié)晶的芯片就誕生了!

芯片設(shè)計(jì)中使用的EDA工具如下:

1、架構(gòu)的設(shè)計(jì)與驗(yàn)證

按照要求,對(duì)整體的設(shè)計(jì)劃分模塊。

架構(gòu)模型的仿真可以使用Synopsys公司的CoCentric軟件,它是基于System C的仿真工具。

2、HDL設(shè)計(jì)輸入

設(shè)計(jì)輸入方法有:HDL語(yǔ)言(Verilog或VHDL)輸入、電路圖輸入、狀態(tài)轉(zhuǎn)移圖輸入。

使用的工具有:Active-HDL,而RTL分析檢查工具有Synopsys的LEDA。

3、前仿真工具(功能仿真)

初步驗(yàn)證設(shè)計(jì)是否滿足規(guī)格要求。

使用的工具有:Synopsys的VCS,Mentor的ModelSim,Cadence的Verilog-XL,Cadence的NC-Verilog。

4、邏輯綜合

將HDL語(yǔ)言轉(zhuǎn)換成門(mén)級(jí)網(wǎng)表Netlist。綜合需要設(shè)定約束條件,就是你希望綜合出來(lái)的電路在面積,時(shí)序等目標(biāo)參數(shù)上達(dá)到的標(biāo)準(zhǔn);邏輯綜合需要指定基于的庫(kù),使用不同的綜合庫(kù),在時(shí)序和面積上會(huì)有差異。邏輯綜合之前的仿真為前仿真,之后的仿真為后仿真。

使用的工具有:Synopsys的Design Compiler,Cadence的 PKS,Synplicity的Synplify等。

5、靜態(tài)時(shí)序分析工具(STA)

在時(shí)序上,檢查電路的建立時(shí)間(Setuptime)和保持時(shí)間(Hold time)是否有違例(Violation)。

使用的工具有:Synopsys的Prime Time。

6、形式驗(yàn)證工具

在功能上,對(duì)綜合后的網(wǎng)表進(jìn)行驗(yàn)證。常用的就是等價(jià)性檢查(Equivalence Check)方法,以功能驗(yàn)證后的HDL設(shè)計(jì)為參考,對(duì)比綜合后的網(wǎng)表功能,他們是否在功能上存在等價(jià)性。這樣做是為了保證在邏輯綜合過(guò)程中沒(méi)有改變?cè)菻DL描述的電路功能。

使用的工具有:Synopsys的Formality

后端相應(yīng)的流程如下

1、數(shù)據(jù)準(zhǔn)備

后端設(shè)計(jì)所需的數(shù)據(jù)主要有是Foundry廠提供的標(biāo)準(zhǔn)單元、宏單元和I/O Pad的庫(kù)文件,它包括物理庫(kù)、時(shí)序庫(kù)及網(wǎng)表庫(kù),分別以.lef、.tlf和.v的形式給出。

前端的芯片設(shè)計(jì)經(jīng)過(guò)綜合后生成的門(mén)級(jí)網(wǎng)表,具有時(shí)序約束和時(shí)鐘定義的腳本文件和由此產(chǎn)生的約束文件以及定義電源Pad的DEF(Design Exchange Format)文件。(對(duì)synopsys 的Astro 而言, 經(jīng)過(guò)綜合后生成的門(mén)級(jí)網(wǎng)表,時(shí)序約束文件 SDC 是一樣的,Pad的定義文件–tdf , .tf 文件 --technology file,Foundry廠提供的標(biāo)準(zhǔn)單元、宏單元和I/O Pad的庫(kù)文件 就與FRAM, CELL view, LM view形式給出(Milkway 參考庫(kù) and DB, LIB file)

2、布局規(guī)劃

主要是標(biāo)準(zhǔn)單元、I/O Pad和宏單元的布局。I/OPad預(yù)先給出了位置,而宏單元?jiǎng)t根據(jù)時(shí)序要求進(jìn)行擺放,標(biāo)準(zhǔn)單元?jiǎng)t是給出了一定的區(qū)域由工具自動(dòng)擺放。布局規(guī)劃后,芯片的大小,Core的面積,Row的形式、電源及地線的Ring和Strip都確定下來(lái)了。如果必要 在自動(dòng)放置標(biāo)準(zhǔn)單元和宏單元之后, 你可以先做一次PNA(power network analysis)–IR drop and EM 。

3、Placement -自動(dòng)放置標(biāo)準(zhǔn)單元

布局規(guī)劃后,宏單元、I/O Pad的位置和放置標(biāo)準(zhǔn)單元的區(qū)域都已確定,這些信息SE(Silicon Ensemble)會(huì)通過(guò)DEF文件傳遞給PC(Physical Compiler),PC根據(jù)由綜合給出的.DB文件獲得網(wǎng)表和時(shí)序約束信息進(jìn)行自動(dòng)放置標(biāo)準(zhǔn)單元,同時(shí)進(jìn)行時(shí)序檢查和單元放置優(yōu)化。如果你用的是PC +Astro,那你可用write_milkway, read_milkway 傳遞數(shù)據(jù)。

4、時(shí)鐘樹(shù)生成(CTS Clock tree synthesis)

芯片中的時(shí)鐘網(wǎng)絡(luò)要驅(qū)動(dòng)電路中所有的時(shí)序單元,所以時(shí)鐘源端門(mén)單元帶載很多,其負(fù)載延時(shí)很大并且不平衡,需要插入緩沖器減小負(fù)載和平衡延時(shí)。時(shí)鐘網(wǎng)絡(luò)及其上的緩沖器構(gòu)成了時(shí)鐘樹(shù)。一般要反復(fù)幾次才可以做出一個(gè)比較理想的時(shí)鐘樹(shù)—Clock skew。

5、STA 靜態(tài)時(shí)序分析和后仿真

時(shí)鐘樹(shù)插入后,每個(gè)單元的位置都確定下來(lái)了,工具可以提出Global Route形式的連線寄生參數(shù),此時(shí)對(duì)延時(shí)參數(shù)的提取就比較準(zhǔn)確了。SE把.V和.SDF文件傳遞給PrimeTime做靜態(tài)時(shí)序分析。確認(rèn)沒(méi)有時(shí)序違規(guī)后,將這來(lái)兩個(gè)文件傳遞給前端人員做后仿真。對(duì)Astro 而言,在detail routing 之后,用starRC XT 參數(shù)提取,生成的SPEF文件傳遞給PrimeTime做靜態(tài)時(shí)序分析,那將會(huì)更準(zhǔn)確。

6、ECO(Engineering Change Order)

針對(duì)靜態(tài)時(shí)序分析和后仿真中出現(xiàn)的問(wèn)題,對(duì)電路和單元布局進(jìn)行小范圍的改動(dòng)。

7、Filler的插入(padfliier, cell filler)

Filler指的是標(biāo)準(zhǔn)單元庫(kù)和I/O Pad庫(kù)中定義的與邏輯無(wú)關(guān)的填充物,用來(lái)填充標(biāo)準(zhǔn)單元和標(biāo)準(zhǔn)單元之間,I/O Pad和I/O Pad之間的間隙,它主要是把擴(kuò)散層連接起來(lái),滿足DRC規(guī)則和設(shè)計(jì)需要。

8、布線(Routing)

布線是指在滿足工藝規(guī)則和布線層數(shù)限制、線寬、線間距限制和各線網(wǎng)可靠絕緣的電性能約束的條件下,根據(jù)電路的連接關(guān)系將各單元和I/O Pad用互連線連接起來(lái),這些是在時(shí)序驅(qū)動(dòng)(Timing driven ) 的條件下進(jìn)行的,保證關(guān)鍵時(shí)序路徑上的連線長(zhǎng)度能夠最小。

9、Dummy Metal的增加

Foundry廠都有對(duì)金屬密度的規(guī)定,使其金屬密度不要低于一定的值,以防在芯片制造過(guò)程中的刻蝕階段對(duì)連線的金屬層過(guò)度刻蝕從而降低電路的性能。加入Dummy Metal是為了增加金屬的密度。

10、DRC和LVS

DRC是對(duì)芯片版圖中的各層物理圖形進(jìn)行設(shè)計(jì)規(guī)則檢查(spacing ,width),它也包括天線效應(yīng)的檢查,以確保芯片正常流片。LVS主要是將版圖和電路網(wǎng)表進(jìn)行比較,來(lái)保證流片出來(lái)的版圖電路和實(shí)際需要的電路一致。DRC和LVS的檢查–EDA工具Synopsy hercules/ mentor calibre/ CDN Dracula進(jìn)行的。Astro also include LVS/DRC check commands。

11、Tape out

在所有檢查和驗(yàn)證都正確無(wú)誤的情況下把最后的版圖GDSⅡ文件傳遞給Foundry廠進(jìn)行掩膜制造,也就是送去流片了。

以上就是本篇的關(guān)于芯片設(shè)計(jì)的全流程介紹,想了解更多EDA相關(guān)信息 歡迎掃碼關(guān)注小F(ID:iamfastone)獲取

- END -

我們有個(gè)IC設(shè)計(jì)研發(fā)云平臺(tái)

集成多種EDA應(yīng)用,大量任務(wù)多節(jié)點(diǎn)并行

應(yīng)對(duì)短時(shí)間爆發(fā)性需求,連網(wǎng)即用

跑任務(wù)快,原來(lái)幾個(gè)月甚至幾年,現(xiàn)在只需幾小時(shí)

5分鐘快速上手,拖拉點(diǎn)選可視化界面,無(wú)需代碼

支持高級(jí)用戶直接在云端創(chuàng)建集群

掃碼免費(fèi)試用,送200元體驗(yàn)金,入股不虧~

更多EDA電子書(shū)

歡迎掃碼關(guān)注小F(ID:iamfastone)獲取

你也許想了解具體的落地場(chǎng)景:

王者帶飛LeDock!開(kāi)箱即用&一鍵定位分子庫(kù)+全流程自動(dòng)化,3.5小時(shí)完成20萬(wàn)分子對(duì)接

這樣跑COMSOL,是不是就可以發(fā)Nature了

Auto-Scale這支仙女棒如何大幅提升Virtuoso仿真效率?

1分鐘告訴你用MOE模擬200000個(gè)分子要花多少錢(qián)

LS-DYNA求解效率深度測(cè)評(píng) │ 六種規(guī)模,本地VS云端5種不同硬件配置

揭秘20000個(gè)VCS任務(wù)背后的“搬桌子”系列故事

155個(gè)GPU!多云場(chǎng)景下的Amber自由能計(jì)算

怎么把需要45天的突發(fā)性Fluent仿真計(jì)算縮短到4天之內(nèi)?

5000核大規(guī)模OPC上云,效率提升53倍

提速2920倍!用AutoDock Vina對(duì)接2800萬(wàn)個(gè)分子

從4天到1.75小時(shí),如何讓Bladed仿真效率提升55倍?

從30天到17小時(shí),如何讓HSPICE仿真效率提升42倍?

關(guān)于為應(yīng)用定義的云平臺(tái):

芯片設(shè)計(jì)五部曲之三 | 戰(zhàn)略規(guī)劃家——算法仿真

芯片設(shè)計(jì)五部曲之二 | 圖靈藝術(shù)家——數(shù)字IC

芯片設(shè)計(jì)五部曲之一 | 聲光魔法師——模擬IC

【案例】速石X騰訊云X燧原:芯片設(shè)計(jì)“存算分離”混合云實(shí)踐

【ICCAD2022】首次公開(kāi)亮相!國(guó)產(chǎn)調(diào)度器Fsched,半導(dǎo)體生態(tài)1.0,上百家行業(yè)用戶最佳實(shí)踐

解密一顆芯片設(shè)計(jì)的全生命周期算力需求

居家辦公=停工?nonono,移動(dòng)式EDA芯片設(shè)計(jì),帶你效率起飛

缺人!缺錢(qián)!趕時(shí)間!初創(chuàng)IC設(shè)計(jì)公司如何“絕地求生”?

續(xù)集來(lái)了:上回那個(gè)“吃雞”成功的IC人后來(lái)發(fā)生了什么?

一次搞懂速石科技三大產(chǎn)品:FCC、FCC-E、FCP

速石科技成三星Foundry國(guó)內(nèi)首家SAFE?云合作伙伴

EDA云平臺(tái)49問(wèn)

億萬(wàn)打工人的夢(mèng):16萬(wàn)個(gè)CPU隨你用

幫助CXO解惑上云成本的迷思,看這篇就夠了

花費(fèi)4小時(shí)5500美元,速石科技躋身全球超算TOP500